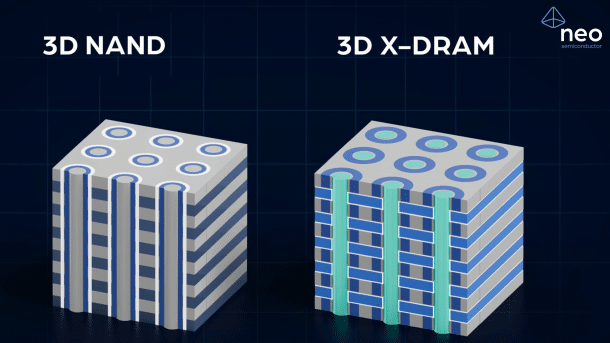

Neo Semiconductor hat "3D X-DRAM" entwickelt, dessen Aufbau 3D-NAND-Flash ähnelt.

(Bild: Neo Semiconductor)

Bei NAND-Flash-Speicher sind Chips mit mehreren internen Funktionslagen – sogenanntes 3D-NAND-Flash – seit Jahren üblich; die aufwendigsten Konstruktionen haben mehr als 200 Lagen. Dynamisches RAM (DRAM) für den Arbeitsspeicher von PCs, Smartphones und Servern ist aber weiterhin "planar" aufgebaut – die einzelnen Speicherzellen liegen nebeneinander, nicht übereinander. Das soll sich bis zum Jahr 2030 ändern, wenn sich die Roadmaps von Speicherherstellern und deren Partnern bewahrheiten.

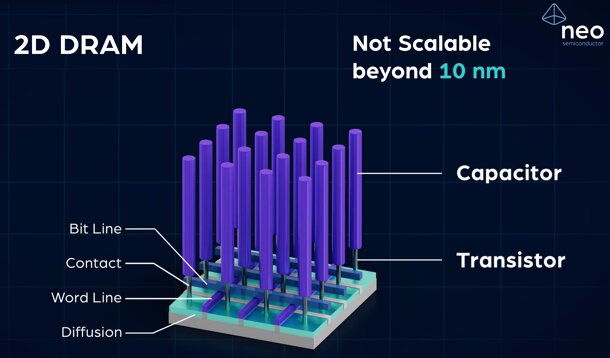

Um die Speicherkapazität eines einzelnen Chips zu steigern, müssen die Entwickler mehr Zellen draufpacken – bei ähnlicher Siliziumfläche, damit die Fertigungskosten im Rahmen bleiben. Eine typische DRAM-Speicherzelle besteht aus einem Transistor (T) und einem Speicherkondensator (C); man spricht auch von 1T1C-Zellen.

Bisher 34.359.738.368 Bit

Derzeit fertigen DRAM-Hersteller einzelne Chips mit maximal 32 Gigabit, also mit 34,36 Milliarden nutzbaren Zellen (235 = 34.359.738.368). Die sind allerdings noch nicht gut lieferbar, anders als 24-GBit-Chips für DIMMs mit 24 und 48 GByte. Die nächsten DRAM-Kapazitätsschritte sind 64 und 128 Gigabit pro Chip, eventuell mit den Zwischenstufen 48 und 96 GBit.

Ein bisschen 3D gibts auch schon bei "planarem" DRAM, die Speicherkondensatoren liegen hier oberhalb der Transistoren.

(Bild: Neo Semiconductor)

Ein bisschen 3D gibt es bei DRAM schon lange: Die Speicherkondensatoren der 1T1C-Zellen sind über oder unter den Transistoren angeordnet, um Platz zu sparen. Die weitere Verkleinerung der einzelnen Zellen wird aus zahlreichen Gründen immer schwieriger. Daher erforschen die DRAM-Hersteller schon seit mehreren Jahren Methoden, um – ähnlich wie bei 3D-NAND-Flash – DRAM-Dies mit mehreren Funktionslagen zu produzieren.

Dabei geht es nicht um mehrere DRAM-Dies, die man nach der Fertigung dünn schleift und übereinanderstapelt wie bei High-Bandwidth Memory (HBM) oder in Multi-Chip-Packages (MCPs). Stattdessen befinden sich bei 3D-DRAM mehrere Lagen übereinander auf demselben (monolithischen) Die. Unabhängig davon kann man mehrere (gedünnte) Dies übereinanderlegen oder komplette Wafer koppeln, um noch höhere Kapazitäten in einem Speicherbaustein zu erreichen.

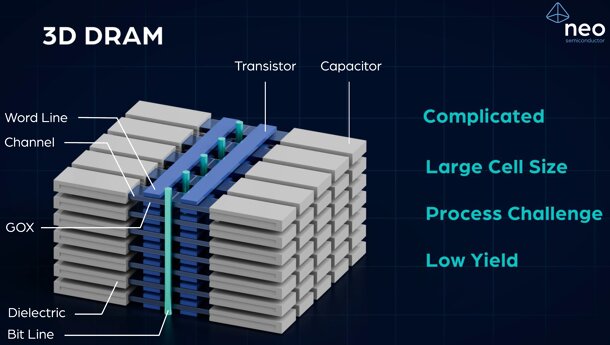

Laut Neo Semiconductor könnte man 3D-DRAM auf diese Weise aufbauen, aber das wäre sehr aufwendig in der Fertigung.

(Bild: Neo Semiconductor)

Die kalifornische Firma Neo Semicondutor zeigte 2023 ihr Konzept für 3D X-DRAM, das ähnlich wie 3D-NAND-Flash konstruiert ist. Neo Semi verzichtet dabei aber auf klassische Speicherkondensatoren innerhalb des Chips und setzt stattdessen auf eine Floating Body Cell als Elektronenspeicher. Mit 230 Lagen sollen 128 Gigabit Kapazität möglich sein.

Zum Vergleich: 3D-NAND-Flash mit 232 Lagen und Triple Level Cells (TLC) speichert bereits 1 Terabit pro Die, weil sich Flash-Zellen kompakter und enger packen lassen. Die Produktion von 3D-NAND mit mehr als 300 Lagen läuft derzeit an.

Samsung-Entwickler präsentierten auf dem 2023 IEEE Symposium on VLSI Technology and Circuits ein Paper zu Vertically Stacked DRAM (VS-DRAM). Außerdem untersucht Samsung die Eignung von Vertical Channel Transistors (VCT) für 3D-DRAM.